Ответы на курс: Архитектура микропроцессоров

Какой микропроцессор первым включил в свой состав все основные блоки, характеризующие архитектуру A-32 ?

|

i 486 |

|

Pentium |

|

i 286 |

|

i 8086 |

Какова особенность системы команд однокристальных микроконтроллеров?

|

использование только простейших режимов адресации операндов |

|

развитая система обработки данных с плавающей запятой |

|

развитая система обработки мультимедийной информации |

Каково основное применение однокристальных микроконтроллеров?

|

решение научно-технических задач |

|

работа в системах управления |

|

построение систем, обеспечивающих эффективную обработку мультимедийной информации |

Каково назначение кэш-памяти?

|

хранение сегмента данных в случае, если его объем не превышает объема внутренней кэш памяти микропроцессора |

|

хранение программы на время ее исполнения в микропроцессоре |

|

хранение наиболее часто используемой информации |

Каковы основные области применения универсальных микропроцессоров?

|

работа в системах управления |

|

построение систем, обеспечивающих эффективную обработку мультимедийной информации |

|

решение научно-технических задач |

Какова область применения сигнальных процессоров?

|

предварительная обработка транзакций при работе с базами данных |

|

цифровая обработка сигналов |

|

системы автоматизированного проектирования |

Как называется первый 64-разрядный микропроцессор фирмы Intel ?

|

Pentium 4 |

|

Pentium MMX |

|

Itanium |

|

Pentium |

Какие модификации в развитии архитектуры IA-32 появились в микропроцессоре Pentium III ?

|

обработки чисел с фиксированной точкой по схеме SIMD |

|

встроенный процессор с плавающей запятой |

|

обработка чисел с плавающей запятой по схеме SIMD |

|

конвейерная обработка информации |

Каковы отличительные черты секционированных микропроцессоров?

|

возможность создавать процессор произвольной разрядности |

|

возможность организации системы прерывания в соответствии с особенностями применения процессора |

|

развитые средства обработки битовой информации |

|

возможность создавать произвольную систему команд вследствие доступа к микропрограммному уровню управления. |

Какие группы регистров НЕ входят в состав регистровой структуры МП с архитектурой IA-32?

|

регистры отладки и тестирования |

|

системные регистры |

|

регистры блока таймеров-счетчиков |

|

регистры блока обработки чисел с плавающей запятой |

|

регистры управления прерыванием |

К какому количеству 16-разрядных регистров возможно обращение в блоке регистров общего назначения МП с архитектурой IA-32?

|

32 |

|

16 |

|

8 |

Какова разрядность регистра LDTR МП с архитектурой IA-32?

|

64 |

|

16 |

|

32 |

|

48 |

Какие флаги входят в состав флагов состояния регистра флагов универсального МП с архитектурой IA 32?

|

флаг переполнения |

|

флаг разрешения маскируемых прерываний |

|

флаг знака |

Каково назначение регистра тегов блока обработки чисел с плавающей запятой в МП с архитектурой IA-32?

|

обеспечить выявление некоторых некорректных операций над данными (при незаполненности соответствующего регистра данных) |

|

расширить разрядность соответствующего регистра данных при возникновении переполнения в арифметических операциях с плавающей запятой |

|

сократить время выполнения операций с плавающей запятой в случае особого состояния регистра данных (ноль, бесконечность) |

Сколько сегментных регистров входит в состав МП с архитектурой IA-32?

|

16 |

|

8 |

|

6 |

|

4 |

К какому количеству 8-разрядных регистров возможно обращение в блоке регистров общего назначения МП с архитектурой IA-32?

|

8 |

|

32 |

|

16 |

Какие регистры НЕ входят в состав FPU микропроцессора с архитектурой IA-32?

|

регистры данных |

|

регистры тэгов |

|

сегментные регистры |

|

регистр состояния |

Сколько разрядов может быть отведено под представление порядка в регистре флагов FPU?

|

10 |

|

7 |

|

22 |

|

определяется состоянием регистра управления FPU |

При каких условиях бит А в элементе таблицы страниц устанавливается в 1?

|

при обращении к странице на чтение |

|

операционной системой по истечении определенного кванта времени |

|

при любом обращении к данной странице |

|

при обращении к странице на запись |

В чем состоит опасность хранения элементов таблиц страниц в TLB?

|

емкость TLB не позволяет хранить достаточно большое количество элементов таблиц страниц для нормального функционирования программы |

|

при модификации ЭТС непосредственно в таблице страниц микропроцессор будет обращаться к странице, используя старую информацию |

|

после модификации информации в странице элемент таблицы страниц не будет отражать реальных сведений об этой странице |

Чем определяется единица измерения длины сегмента, задаваемой в его дескрипторе?

|

битом D дескриптора сегмента |

|

битом G дескриптора сегмента |

|

битом PG регистра CR0 |

Какова длина поля предела в дескрипторе сегмента?

|

20 |

|

8 |

|

16 |

|

32 |

|

64 |

Что входит в состав логического адреса при страничной организации логического адресного пространства?

|

идентификатор страницы |

|

смещение в странице |

|

смещение в сегменте |

|

идентификатор сегмента |

|

смещение от начала адресного пространства |

Какова длина поля адреса в элементе каталога таблиц страниц?

|

16 |

|

10 |

|

20 |

|

13 |

Как определяется положение дескриптора в локальной таблице дескрипторов относительно ее начала?

|

по смещению, определяемому режимом адресации для операндов и регистром EIP для команд |

|

по содержимому поля INDEX селектора |

|

по содержимому поля ПРЕДЕЛ дескриптора |

Что такое физическое адресное пространство?

|

массив адресуемых элементов, организованный в виде определенной структуры, определяемой прикладным программистом в зависимости от особенностей структуры данных своей программы |

|

массив адресуемых элементов, организованный в виде определенной структуры, задаваемой системным программистом |

|

одномерный массив элементов, каждому из которых присвоен свой номер, называемый адресом |

Каково назначение поля предела в регистре GDTR?

|

указание длины глобальной таблицы дескрипторов |

|

указание размерности дескрипторов, размещенных в GDT |

|

указание положения дескриптора сегмента состояния задачи, активной в данной момент |

Меняется ли объем страницы в разных моделях микропроцессоров?

|

каждая модель микропроцессора имеет свой объем страницы |

|

нет, он всегда постоянен и равен 4 Кбайт |

|

да, объем страницы может изменяться, но каждая страница имеет постоянный объем. |

Как определяется положение начала каталога таблиц страниц?

|

по содержимому поля TABLE регистра флагов |

|

по содержимому регистра CR3 |

|

по содержимому регистра CR0 |

|

по содержимому нулевого дескриптора глобальной таблицы дескрипторов |

Для каких целей используется поле масштаба SIB-байта в формате команд адреса МП с архитектурой IA 32?

|

увеличение количества режимов адресации |

|

обеспечение возможности масштабирования индексного регистра при вычислении смещения в сегменте |

|

обеспечение возможности изменения размера операнда, установленного по умолчанию в дескрипторе данного сегмента |

Каково назначение бита D в дескрипторе сегмента?

|

разрешение кэширования сегмента |

|

указание единицы измерения длины сегмента |

|

определение присутствия сегмента в оперативной памяти |

|

определение размерности операндов по умолчанию |

Какое главное назначение имеют сегменты при сегментно-страничной организации логического адресного пространства?

|

обеспечение возможности кэширования информации |

|

создание виртуальной памяти |

|

обеспечение потребностей прикладного программиста |

Что получается в результате сегментного преобразования адреса?

|

смещение в странице |

|

физический адрес |

|

логический адрес |

|

номер виртуальной страницы |

|

линейный адрес |

Какова длина сегмента в МП с архитектурой IA 32, работающего в защищенном режиме?

|

переменная от 1 байта до 16Кб |

|

16Кб |

|

переменная от 1 байта до 232 байт |

|

переменная от 16К байт до 232 байт |

По какому физическому адресу расположен дескриптор сегмента, если в его селекторе значение поля индекса равно 4, бит TI=0, а базовый адрес в регистре глобальной таблицы дескрипторов GDTR равен 00010000h?

|

00010020h |

|

обращение будет проходить к локальной таблице дескрипторов через дескриптор LDT, который извлекается из дескриптора 3 глобальной таблицы дескрипторов |

|

00010004h |

Почему виртуальная память строится на основе страничной, а не сегментной организации памяти?

|

так как объем страницы всегда меньше объема сегмента |

|

так как объем страницы всегда больше объема сегмента |

|

так как страницы имеют переменный объем, а сегменты фиксированный |

|

так как страницы имеют фиксированный объем, а сегменты переменный |

Какие адреса использует программист при составлении программ?

|

физические |

|

используемая система адресов устанавливается программистом самостоятельно |

|

виртуальные |

Сколько обращений к памяти требуется при вычислении линейного адреса в случае нахождения дескриптора сегмента в локальной таблице дескрипторов?

|

2 |

|

3 |

|

1 |

|

4 |

Что входит в состав логического адреса микропроцессора с архитектурой IA-32?

|

смещение в странице |

|

смещение в сегменте |

|

селектор |

|

номер виртуальной страницы |

Каково назначение бита G в дескрипторе сегмента?

|

включение механизма страничного преобразования адреса |

|

разрешение кэширования сегмента |

|

указание единицы измерения длины сегмента |

Какие дополнительные возможности по адресации операндов имеет МП с архитектурой IA 32 по сравнению с универсальным 16-разрядным микропроцессором?

|

обеспечение возможности использования любого из регистров общего назначения при формировании смещения в сегменте |

|

обеспечение возможности масштабирования индексного регистра при вычислении смещения в сегменте |

|

обеспечение возможности замены сегментного регистра, используемого по умолчанию для заданного режима адресации |

Какая информация содержится в глобальной таблице дескрипторов?

|

дескрипторы таблиц страниц всех задач, выполняемых в процессоре |

|

дескрипторы сегментов, доступных всем задачам, выполняемым в процессоре |

|

дескрипторы сегментов, доступных только задаче, выполняемой в данный момент |

|

дескриптор каталога таблицы страниц |

Какое главное назначение имеют страницы при сегментно-страничной организации логического адресного пространства?

|

обеспечение потребностей прикладного программиста в логической памяти постоянной длины |

|

обеспечение возможности кэширования информации |

|

создание виртуальной памяти |

Какова длина поля адреса в дескрипторе сегмента?

|

64 |

|

8 |

|

16 |

|

32 |

Как определяется положение начала локальной таблицы дескрипторов?

|

по содержимому поля адрес дескриптора сегмента локальной таблицы дескрипторов, находящемуся в глобальной таблице дескрипторов |

|

по содержимому регистра LDTR |

|

по содержимому регистра GDTR |

Какие типы системных объектов могут быть описаны в дескрипторе сегмента?

|

сегмент кэш-памяти |

|

сегмент локальной таблицы дескрипторов |

|

сегмент состояния задачи |

|

сегмент таблицы страниц |

Какая информация хранится в кэш-памяти при включении компьютера?

|

все строки кэш-памяти недостоверны |

|

заполненные строки по результатам тестовых прогонов программы |

|

заполненные строки по результатам предыдущего сеанса работы |

Каковы отличительные черты кэш-памяти с обратной записью?

|

обновление оперативной памяти производится сразу же после изменения информации в кэш-памяти |

|

обновление оперативной памяти производится только при вытеснении измененной строки кэш-памяти |

|

обновление оперативной памяти производится в момент заполнения буфера, хранящего все измененные строки кэш-памяти |

Какая организация кэш-памяти называется множественно ассоциативной?

|

если каждый блок ОЗУ может размещаться по ограниченному множеству мест в кэш-памяти |

|

если каждый блок ОЗУ имеет только одно фиксированное место, по которому он может размещаться в кэш-памяти |

|

если каждый блок ОЗУ может размещаться в произвольном месте кэш-памяти |

Каково назначение кэш-памяти?

|

хранение команд, наиболее часто используемых при выполнении программы |

|

хранение данных, наиболее часто используемых при выполнении программы |

|

хранение программы начальной загрузки компьютера |

С какой целью шина адреса микропроцессора делается двунаправленной?

|

для того, чтобы микропроцессор отслеживал обращение со стороны других микропроцессоров за информацией, хранящейся в его кэш-памяти |

|

для использования его кэш-памяти другими микропроцессорами с целью сокращения их времени доступа к информации |

|

для записи информации в режиме прямого доступа к памяти |

Как организована внутренняя кэш-память в микропроцессоре I486?

|

используется только кэш-память команд |

|

общая для команд и данных |

|

используется только кэш-память данных |

|

раздельная для команд и данных |

К какому типу относится внутренняя кэш-память в микропроцессоре I486?

|

полностью ассоциативная |

|

с прямым отображением |

|

множественно-ассоциативная |

Какая информация хранится в блоке тэгов кэш-памяти?

|

признак достоверности строки данных |

|

старшие разряды физического адреса |

|

признаки, отмечающие строку кэш-памяти, к которой дольше всего не было обращений |

|

младшие разряды физического адреса |

Возможно ли выполнение команд ввода-вывода для программы, чей уровень привилегий меньше уровня привилегий, указанного в поле IOPL регистра флагов?

|

да, при использовании шлюза вызова |

|

нет |

|

да, если обращение к этому устройству разрешено в битовой карте ввода-вывода сегмента состояния задачи. |

Какое количество уровней привилегий различается аппаратными средствами микропроцессора на уровне страниц?

|

3 |

|

4 |

|

2 |

В каком случае часть сегмента может иметь особую защиты по отношению ко всему сегменту?

|

при использовании специального механизма граничных регистров для отдельных блоков сегмента |

|

никогда |

|

Если это определено на уровне страниц, на которые разбит сегмент |

На каком уровне привилегий работают программы ядра операционной системы?

|

2 |

|

1 |

|

3 |

|

0 |

Какое максимальное количество уровней привилегий различается аппаратными средствами микропроцессора?

|

8 |

|

3 |

|

4 |

|

2 |

Каким образом программе обеспечивается возможность вызова более привилегированных программ?

|

путем размещения в доступной ей таблице дескрипторов шлюза вызова более привилегированной программы |

|

такие вызовы производятся программами ядра операционной системы или утилитами ОС |

|

такие вызовы производятся только программами ядра операционной системы |

На каком уровне привилегий могут располагаться данные, к которым разрешено обращение программе?

|

на том же и более высоком уровнях |

|

на том же и более низком уровнях |

|

на любом уровне |

|

только на том же уровне |

Какой уровень привилегий кодируется в поле DPL байта доступа шлюза вызова?

|

Это поле всегда равно 3 |

|

уровень привилегий вызываемой задачи |

|

уровень привилегий задач, которым разрешается обращение через этот шлюз вызова |

Какие команды относятся к привилегированным?

|

команды обмена с регистрами управления |

|

команды загрузки таблиц дескрипторов |

|

команды ввода-вывода |

Как изменит повышение приоритета одной из программ пропускную способность мультипрограммной ЭВМ?

|

может привести как к повышению, так и к понижению пропускной способности |

|

повысит |

|

снизит |

Для чего используется бит занятости B в дескрипторе TSS?

|

для предотвращения возможности повторного вызова задачи, выполнение которой прервано |

|

для обеспечения правильного возврата к предыдущей задаче по команде IRET |

|

для указания типа дескриптора TSS |

Какую длину имеет сегмент состояния задачи?

|

4К байт |

|

8 байт |

|

переменную, но не выше 232 байт |

|

переменную, но не менее 104 байт |

Какое максимальное количество источников прерываний может быть подключено к универсальному микропроцессору с использованием контроллеров приоритетных прерываний типа i8259 ?

|

8 |

|

произвольное количество |

|

64 |

|

15 |

Чем выполнение программы — обработчика прерывания отличается от выполнения подпрограмм?

|

вызов подпрограммы проводится командами типа CALL, а переход на обработчик прерывания происходит с помощью команд безусловного перехода |

|

программа — обработчик прерывания всегда оформляется как новая задача |

|

вызов подпрограммы кодируется программистом в своей программе, а обработчик прерывания вызывается аппаратными средствами микропроцессора при возникновении особой ситуации в работе компьютера |

Какую информацию содержит тип прерывания?

|

приоритет запроса прерывания |

|

номер дескриптора в таблице дескрипторов прерываний |

|

адрес обработчика прерывания |

Как определяется адрес обработчика прерываний для универсального микропроцессора, работающего в реальном режиме?

|

адрес вводится в МП по шине данных из контроллера приоритетных прерываний |

|

по таблице дескрипторов прерываний |

|

по таблице векторов прерываний |

Сколько типов прерываний используется в универсальном микропроцессоре?

|

32 |

|

8 |

|

16 в 16-разрядном МП и 32 в 32-разрядном МП |

|

256 |

Как определяется начальный адрес блока ОЗУ, с которым проводит обмен внешнее устройство в режиме прямого доступа к памяти?

|

передается от микропроцессора после получения им сигнала запроса на прямой доступ от контроллера ПДП |

|

передается от внешнего устройства после получения им сигнала DACK подтверждения прямого доступа |

|

загружается в контроллер ПДП при его инициализации |

Как в МПС устраняется возможность зависания в случае повреждения линии, по которой в микропроцессор поступает сигнал готовности внешнего устройства?

|

при отсутствии сигнала готовности за установленное время микропроцессор генерирует запрос к внешнему устройству на считывание состояния внешнего устройства по шине данных |

|

так как быстродействие всех модулей, составляющих МПС, должно быть сбалансировано, то по истечении максимально установленного времени обмен считается корректно завершенным |

|

если данный сигнал не поступает в МП за установленное время, то вырабатывается сигнал прерывания по ошибке ввода/вывода |

Какие из параметров НЕ входят в понятие интерфейса?

|

алгоритмы передачи сигналов |

|

режимы адресации команд ввода-вывода |

|

правила интерпретации сигналов устройствами |

|

схемы согласования уровней сигналов |

Каковы недостатки магистрально-модульного способа организации микропроцессорных систем?

|

высокая сложность удаления из состава МПС отдельных модулей |

|

необходимость использования микропроцессоров только определённых моделей |

|

высокая сложность добавления в состав МПС нового оборудования |

|

ограничения производительности МПС из-за невозможности одновременного взаимодействия более двух модулей в системе |

Какие из перечисленных сигналов используются при обмене информации в режиме прямого доступа к памяти?

|

DACKi |

|

DRQi |

|

IRQi |

Каков основной недостаток обмена информацией в режиме прямого доступа к памяти?

|

процедура первоначальной инициализации контроллера ПДП занимает значительное время, что нерационально при передаче небольших блоков информации |

|

обмен может проводиться лишь блоками фиксированной длины |

|

нерациональное использование мощности микропроцессора |

|

каждое устройство ввода-вывода может проводить обмен лишь с фиксированными областями оперативной памяти |

При выполнении каких команд на магистрали МПС формируется сигнал IOWR?

|

только при выполнении микропроцессором команды OUT |

|

при выполнении микропроцессором любой команды обращения к внешнему устройству или памяти |

|

при выполнении микропроцессором любой команды обращения к внешнему устройству |

Возможно ли изменение приоритетов в обслуживании внешних устройств в режиме ПДП?

|

да |

|

нет, так как в этом режиме в микропроцессорной системе может быть подключено лишь одно внешнее устройство |

|

нет, так как он определяется аппаратным подключение внешних устройств к контроллеру ПДП |

Каково время выполнения 100 команд в идеальном 5 ступенчатом конвейере при длительности такта 10 нс?

|

500 нс |

|

5000 нс |

|

1040 нс. |

Чем определяется длительность такта работы микропроцессора при конвейерной обработке информации?

|

длительностью самого длинного этапа выполнения команды при последовательной обработке |

|

длительностью самого короткого этапа выполнения команды при последовательной обработке |

|

имеющимися на данный момент технологическими возможностями производства микропроцессорных БИС |

Какова длительность выполнения 5 команд в идеальном 5 ступенчатом конвейере при длительности такта 10 нс?

|

90 нс |

|

70 нс |

|

50 нс |

Каким образом, в основном, разрешаются конфликты типа RAW?

|

дублированием ресурсов |

|

методом продвижения данных |

|

введением блока предсказания переходов |

Какие показатели работы программы улучшаются при использовании схемы «задержанных переходов»?

|

время, необходимое для формирования истинного условия перехода, используются для выполнения полезных команд программы |

|

ликвидируются конфликты по данным |

|

ликвидируются конфликты по управлению |

Какова длительность выполнения 3 команд в идеальном 5 ступенчатом конвейере при длительности такта 10 нс?

|

70 нс |

|

150 нс |

|

30 нс |

Как называются конфликты в конвейере, возникающие при конвейеризации команд переходов?

|

по данным |

|

структурные |

|

по управлению |

Каковы основные особенности программ мультимедийной обработки?

|

алгоритмы, не требующие интенсивных вычислений |

|

операции с высоким уровнем параллелизма |

|

данные целого типа небольшой разрядности |

|

короткие циклы с высоким коэффициентом повторяемости |

|

сильная зависимость между результатами выполнения отдельных операций |

Какую роль играют порты в микроархитектуре микропроцессора Pentium 4 ?

|

расширяют возможности взаимодействия микропроцессора с внешними устройствами в режиме прямого доступа к памяти |

|

используются для расширения количества внешних устройств, подключаемых к микропроцессору |

|

распределяют микрокоманды из очереди микрокоманд по исполнительным устройствам |

Какие новые типы данных используют MMX-команды?

|

несколько однотипных операндов упакованных в одно 64 разрядное слово |

|

числа с плавающей запятой повышенной разрядности |

|

числа с фиксированной точкой повышенной разрядности |

Какова схема обработки данных по технологии ММХ?

|

одна команд — один операнд |

|

множество команд — множество данных |

|

одна команда — множество данных |

Какие особенности микропроцессора Pentium 4 играют наиболее важную роль при определении скорости обмена с памятью запросов длиной до 64 байт?

|

учетверенная результирующая частота передачи данных |

|

высокая частота тактирования шины |

|

наличие интегрированной на кристалле микропроцессора кэш-памяти второго уровня |

Каковы особенности блок распределения микрокоманд микропроцессора Pentium 4?

|

выборка микрокоманд из очереди по мере готовности операндов, после чего микрокоманды ставятся в локальные очереди к соответствующим исполнительным устройствам |

|

выборка микрокоманд из очереди по мере готовности соответствующих операндов и исполнительных устройств |

|

выборка микрокоманд из очереди происходит строго в порядке их поступления, обеспечивая корректное завершение командной последовательности |

Каковы недостатки повышения производительности микропроцессоров только за счет увеличения тактовой частоты?

|

так как повышение тактовой частоты требует увеличения количества исполнительных устройств в микропроцессоре, то это приводит к значительному увеличению конфликтов по данным |

|

существенное повышение тактовой частоты микропроцессора требует использование памяти с таким высоким быстродействием, которое невозможно на данном технологическом уровне |

|

так как повышение тактовой частоты достигается увеличением длины конвейера, то такой путь приводит к большим потерям времени при необходимости перезагрузки конвейера |

Какие блоки входят в состав процессорного элемента микропроцессора Polaris?

|

маршрутизатор |

|

вычислитель |

|

сетевой адаптер |

По каким направлениям традиционно шло повышение производительности микропроцессоров?

|

увеличение количества исполнительных устройств в микропроцессоре |

|

создание универсальных исполнительных устройств для выполнения любых команд из системы команд |

|

повышение тактовой частоты работы МП |

Какие блоки входят в состав вычислителя процессорного элемента микропроцессора Polaris?

|

таймер/счетчик |

|

целочисленное АЛУ |

|

устройства для выполнения операций умножения с накоплением |

|

память команд |

|

память данных |

Какова длина конвейера микропроцессора Power4??

|

11 |

|

15 |

|

21 |

|

8 |

Какими аппаратными средствами обеспечивается поддержка RISC-архитектуры?

|

большое количество внутренних регистров |

|

длина конвейера, превосходящая конвейеры в CISC-микропроцессорах |

|

трехадресная система команд |

|

большая емкость кэш-памяти |

|

простейшие режимы адресации |

Каковы особенности использования кэш-памяти третьего уровня в микропроцессоре Power4?

|

общий для всех микропроцессоров микросхемного модуля |

|

содержится в каждом ядре микропроцессора |

|

на кристалле микропроцессора Power4 содержатся только тэги кэш-памяти третьего уровня |

|

содержится в каждом кристалле микропроцессора Power4 |

Какой из типов вычислительной системы обладает наименьшей связностью общих ресурсов?

|

системы с массовой параллельной обработкой |

|

кластеры |

|

системы с симметричной мультипроцессорной обработкой |

|

системы с неоднородным доступом к памяти |

Чем определяются основные ограничения на рост производительности SMP-систем?

|

пропускной способностью магистрали |

|

производительностью процессоров, составляющих SMP-систему |

|

необходимостью иметь в составе системы только однотипные процессоры |

Каковы основные черты систем с симметричной мультипроцессорной обработкой?

|

все процессоры, составляющие систему, имеют равноправный доступ ко всему пространству оперативной памяти и ввода-вывода |

|

система состоит из отдельных полностью независимых компьютеров, соединенных высокоскоростной магистралью или коммутатором |

|

система состоит из нескольких компьютеров, имеющих общие разделяемые ресурсы |

|

каждый процессор системы имеет свое пространство оперативной памяти и ввода-вывода, но с помощью специальной логики может обратиться к ресурсам любого другого узла |

Какой фирмой был разработан и запатентован первый транспьютер?

|

Фирма INMOS |

|

Intel |

|

AMD |

|

MIPS Technology |

Каковы основные черты MPP-систем?

|

каждый процессор системы имеет свое пространство оперативной памяти и ввода-вывода, но с помощью специальной логики может обратиться к ресурсам любого другого узла |

|

все процессоры, составляющие систему, имеют равноправный доступ ко всему пространству оперативной памяти и ввода-вывода |

|

система состоит из нескольких компьютеров, имеющих общие разделяемые ресурсы |

|

система состоит из отдельных полностью независимых компьютеров, соединенных высокоскоростной магистралью или коммутатором |

Что такое транспьютер?

|

микропроцессор со встроенными средствами межпроцессорной коммуникации, предназначенными для построения многопроцессорных систем |

|

БИС, входящая в состав чипсета и обеспечивающая взаимодействие микропроцессоров при межпроцессорном обмене |

|

многопроцессорная система, в которой каждый процессор имеет равноправный доступ к общей оперативной памяти |

В каких случаях в МК-51 возможны вложенные прерывания?

|

если уровень прерывания нового запроса выше уровня прерывания обрабатываемого запроса, установленного в регистре IP |

|

если при аппаратном опросе флагов запросов прерывания новый запрос опрашивается раньше |

|

вложенные прерывания невозможны |

Как микроконтроллер выбирает запрос на обслуживание в случае одновременного поступления нескольких запросов прерываний МК-51?

|

микроконтроллер откладывает обработку прерывания до тех пор, пока инициаторы прерывания не снимут все свои запросы, кроме одного. Проверка состояния запросов проводится в каждом машинном цикле. |

|

одновременное поступление нескольких запросов прерываний невозможно |

|

выбирается запрос с наиболее высоким приоритетом, установленном в регистре приоритетов, а при их равенстве — согласно аппаратно установленному порядку опроса флагов запросов прерываний |

Система команд какого типа микропроцессоров обычно содержит большее количество режимов адресации?

|

однокристальных микроконтроллеров |

|

зависит не от типа микропроцессора, а от конкретной модели |

|

универсальных микропроцессоров |

Какова разрядность однокристального микроконтроллера МК-51?

|

16 |

|

64 |

|

8 |

|

32 |

Какова частота машинного цикла микроконтроллера МК-51, если его внешняя частота равна 12 МГц?

|

6 МГц |

|

12 МГц |

|

1 МГц |

|

2 МГц |

Какое значение будут иметь регистры TL0 и TH0 таймера/счетчика, работающего в режиме 2 счета внешних событий, после поступления на его счетный вход 6 импульсов, если их начальное состояние следующее: TL0 = 252; TH0= 252 ?

|

TL0 = 2; TH0= 251 |

|

TL0 = 258; TH0= 252 |

|

TL0 = 254; TH0= 252 |

|

TL0 = 2; TH0= 252 |

Через какой промежуток времени таймер-счетчик T/C0 микроконтроллера МК-51, работающего на тактовой частоте 12 МГц в режиме, обеспечивающем 16-разрядный счет, выдаст сигнал запроса прерывания, если его начальное состояние следующее: TH0=FFh, TL0=F5h ?

|

5 мкс |

|

11 мкс |

|

10 мкс |

|

6 мкс |

Каким образом таймер-счетчик отсчитывает интервалы времени?

|

увеличением своего значения в каждом цикле внешней синхронизации |

|

уменьшением своего значения в каждом цикле внешней синхронизации |

|

увеличением своего значения в каждом машинном цикле |

|

уменьшением своего значения в каждом машинном цикле |

Какое значение будут иметь регистры TL0 и TH0 таймера/счетчика, работающего в режиме 2 счета внешних событий, после поступления на его счетный вход 10 импульсов, если их начальное состояние следующее: TL0 = 250; TH0= 250 ?

|

TL0 = 260; TH0= 250 |

|

TL0 = 4; TH0= 251 |

|

TL0 = 254; TH0= 250 |

|

TL0 = 4; TH0= 250 |

Какое количество источников прерываний используется в микроконтроллере МК-51?

|

4 |

|

3 |

|

2 |

|

5 |

|

8 |

Каковы условия корректного выполнения программно-управляемого обмена информацией в МПС?

|

микроконтроллер при возникновении необходимости обращается к ВУ и производит обмен информацией, проверяя перед этим состояние готовности внешнего устройства |

|

микроконтроллер при возникновении необходимости обращается к внешнему устройству и производит обмен информацией. |

|

микроконтроллер при возникновении необходимости обращается к ВУ и производит обмен информацией, однако при этом программа МК должна быть составлена таким образом, чтобы к моменту обмена внешнее устройство было безусловно к нему готово. |

Каким образом микропроцессор может корректно выполнить обмен информацией с внешним устройством, не проверяя состояние его готовности?

|

внешнее устройство само сообщает микропроцессору о своей готовности к обмену сигналом запроса прерывания |

|

МП определяет максимальное время, необходимое для перехода внешнего в состояние готовности, после воздействия на него со стороны микропроцессора, по истечении которого выполняет обмен |

|

мП выполняет ввод/вывод информации согласно заложенной в него программе, при этом обеспечение корректности обмена возлагается на внешнее устройство |

При каких условиях обмен по прерыванию эффективнее других способов обмена?

|

в случае, когда микропроцессор помимо работы с внешним устройством решает другие задачи не в реальном масштабе времени |

|

в случае частых запросов прерываний, реакция на которые может проходить не в реальном масштабе времени |

|

в случае, когда основная задача микропроцессора — быстро выполнить обмен информацией с внешним устройством, готовым к обмену |

|

в случае редких запросов прерываний, требующих быстрой реакции микропроцессора |

Каким образом вычисляются параметры гармоник, составляющих дискретный сигнал?

|

прямым преобразованием Фурье |

|

Фазовый сдвиг гармоник вычисляется прямым преобразованием Фурье, а амплитуды гармоник обратным преобразованием |

|

амплитуды гармоник вычисляются прямым преобразованием Фурье, а фазовый сдвиг — обратным преобразованием |

|

обратным преобразованием Фурье |

Каковы особенности системы команд процессоров ЦОС?

|

наличие команд обработки информации по схеме SIMD |

|

наличие команд битовой арифметики |

|

размещение операндов большинства команд в регистрах |

|

наличие команд умножения с накоплением |

Какие действия выполняются при преобразовании Фурье?

|

преобразование аналогового сигнала в цифровую форму |

|

преобразование аналогового сигнала из вида амплитуда-время к виду частота-амплитуда |

|

преобразование аналогового сигнала из вида частота-амплитуда к виду амплитуда-время |

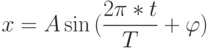

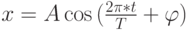

Какое выражение гармонического колебания называется гармоникой?

Какие средства используются для автономной разработки и отладки программного обеспечения микропроцессорных систем?

|

симуляторы |

|

компиляторы |

|

текстовые редакторы |

|

логические анализаторы |

Каковы функции эмулятора ПЗУ?

|

замена внутреннего ПЗУ микроконтроллера оперативной памятью при отладке |

|

замена внутреннего ОЗУ данных микроконтроллера постоянной памятью при отладке |

|

замена внешнего ПЗУ микропроцессорной системы оперативной памятью при отладке |

|

замена внешнего ОЗУ микропроцессорной системы постоянной памятью при отладке |

Каковы основные особенности МПС как объектов контроля?

|

шинная организация |

|

высокое быстродействие МПС |

|

необходимость контроля МПС при всех возможных сочетаниях состояния внутренних регистров БИС |

|

высокая сложность БИС |

Каковы особенности контроля работоспособности МПС в процессе эксплуатации?

|

высокая производительность контрольно-измерительной аппаратуры |

|

портативность контрольно-измерительной аппаратуры |

|

высокая автоматизация процесса контроля |

Каковы достоинства JTAG эмулятора?

|

низкая стоимость средства отладки |

|

максимально точное соответствие условий отладки рабочим условиям серийного изделия |

|

возможность использования в микроконтроллерах, имеющих внутреннюю память программ любого типа (ПЗУ, ППЗУ, Flash) |

|

возможность одновременного тестирования нескольких устройств |

На каком языке написано большинство программ, входящих в состав тестов SPEC для оценки производительности на целочисленных операциях?

|

Си++ |

|

Фортран |

|

Си |

Каким образом в настоящее время оценивается производительность микропроцессоров и микропроцессорных систем?

|

с помощью специальных тестовых программ — бэнчмарков |

|

по тактовой частоте работы микропроцессора совместно с указанием фирмы-производителя |

|

по количеству операций, выполняемых в единицу времени |

Какие действия по цифровой обработке сигналов играют главную роль в оценке производительности сигнальных микропроцессоров в тестах BDTI?

|

выполнение операций «умножение с накоплением» |

|

цифровая фильтрация |

|

быстрое преобразование Фурье |

В чём заключается основное отличие тестовой программы Linpack от оценки производительности в MIPS и MFLOPS?

|

оценка производительности выполняется в относительных единицах по отношению к результатам, получаемым на «эталонной» машине, при этом полученные результаты корректируются с учетом тактовой частоты работы МП |

|

оценка производительности выполняется в MIPS и MFLOPS, но при выполнении конкретной практической задачи |

|

оценка производительности выполняется в относительных единицах по отношению к результатам, получаемым на «эталонной» машине |

Какие характеристики вычислительной системы оценивают тесты SPECcpu?

|

оценка производительности при обработке транзакций |

|

оценка производительности на целочисленных операциях |

|

оценка производительности на операциях с плавающей точкой |

На каком уровне привилегий могут выполняться привилегированные команды?

|

на 3-м |

|

на любом, кроме 3-го |

|

на 0-м |

|

на любом, кроме 0-го |

Чем характеризуются программные прерывания (исключения) типа ЛОВУШКА?

|

обнаруживаются после выполнения команды, приведшей к ошибке, вызвавшей прерывание |

|

рестарт программы происходит с повторного выполнения команды, вызвавшей прерывание |

|

при возникновении прерывания данного типа программа снимается с обработки |

|

обнаруживаются до возникновения фактической ошибки при выполнении команды |

|

причину ошибки, вызвавшей прерывание, установить невозможно |

|

рестарт программы происходит с команды, следующей за командой, вызвавшей прерывание |

Какие действия по обработке прерывания микропроцессор выполняет автоматически при поступлении запроса прерывания, разрешенного к обслуживанию?

|

сохранение контекста прерываемой программы |

|

формирование таблицы векторов прерываний |

|

формирование таблицы дескрипторов прерываний |

|

определение адреса обработчика прерывания по типу поступившего запроса прерывания |

Как определяются приоритеты запросов прерываний в контроллере приоритетных прерываний?

|

приоритеты запросов циклически сдвигаются после обработки очередного запроса |

|

в процессе работы компьютера специальными командами управления устанавливается наиболее приоритетный запрос. Приоритеты остальных запросов циклически сдвигаются относительно установленного. |

|

возможен любой из вариантов назначения приоритетов в зависимости от настроек контроллера |

|

всегда наиболее приоритетный запрос ? IRQ0, а наименее приоритетный ? IRQ7 |

Каковы причины возникновения структурных конфликтов в конвейере?

|

недостаточное дублирование некоторых ресурсов |

|

зависимость выполнения одной команды от результата выполнения предыдущей команды |

|

некоторые ступени отдельных команд выполняются более одного такт |

Добавить комментарий

Для отправки комментария вы должны авторизоваться.