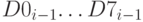

Ответы на курс: Основы цифровой техники

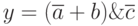

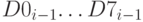

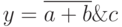

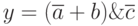

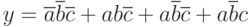

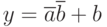

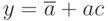

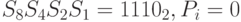

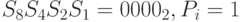

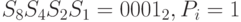

Для заданной схемы выбрать соответствующую таблицу истинности

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

0 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

0 |

|

Выбрать карту Карно, соответствующую минимальному логическому выражению

|

|

|

bc |

|

|

10 |

00 |

01 |

11 |

| a |

0 |

1 |

1 |

0 |

1 |

| 1 |

0 |

0 |

0 |

0 |

|

|

|

|

bc |

|

|

10 |

00 |

01 |

11 |

| a |

0 |

0 |

0 |

1 |

1 |

| 1 |

1 |

1 |

1 |

1 |

|

|

|

|

bc |

|

|

10 |

00 |

01 |

11 |

| a |

0 |

0 |

0 |

1 |

0 |

| 1 |

1 |

1 |

1 |

1 |

|

|

|

|

bc |

|

|

10 |

00 |

01 |

11 |

| a |

0 |

1 |

0 |

0 |

1 |

| 1 |

1 |

1 |

1 |

0 |

|

Для заданной схемы выбрать соответствующую таблицу истинности

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

0 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

0 |

|

Выбрать минимальное логическое выражение, соответствующее карте Карно

|

|

bc |

|

|

10 |

00 |

01 |

11 |

| a |

0 |

1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

1 |

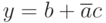

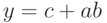

Напишите логическое выражение для схемы:

Выберите схему, соответствующую логическому выражению

Выбрать максимальное логическое выражение, соответствующее таблице истинности

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

0 |

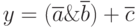

Выбрать минимальное логическое выражение, соответствующее карте Карно

|

|

bc |

|

|

10 |

00 |

01 |

11 |

| a |

0 |

1 |

1 |

1 |

1 |

| 1 |

0 |

1 |

0 |

0 |

Выбрать правильную таблицу истинности для выражения:

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

0 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

0 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

1 |

|

Для заданной схемы выбрать соответствующую таблицу истинности

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

0 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

0 |

|

Выбрать таблицу истинности, соответствующую канонической сумме минтермов

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

1 |

| 0 |

0 |

1 |

1 |

| 0 |

1 |

0 |

1 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

|

|

| a |

b |

c |

y |

| 0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

0 |

| 0 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

1 |

|

Выберите тип дешифратора по таблице истинности:

| Входы |

Выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

| 0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

| 0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

| 0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

| 0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

| 0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

| 0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

| 0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

дешифратор на 16 выходов с прямыми входными и инверсными выходными сигналами. |

|

дешифратор на четыре входа с прямыми входными и инверсными выходными сигналами. |

|

дешифратор на четыре входа с прямыми входными и выходными сигналами. |

|

дешифратор на четыре выхода с инверсными входными и выходными сигналами. |

Выберите УГО для функциональной схемы дешифратора:

Выберите таблицу истинности, соответствующую дешифратору на два входа с инверсными входами и прямыми выходами:

|

| Входы |

Выходы |

|

|

|

|

|

|

| 0 |

0 |

0 |

1 |

1 |

1 |

| 0 |

1 |

1 |

0 |

1 |

1 |

| 1 |

0 |

1 |

1 |

0 |

1 |

| 1 |

1 |

1 |

1 |

1 |

0 |

|

|

| Входы |

Выходы |

|

|

|

|

|

|

| 0 |

0 |

1 |

1 |

1 |

0 |

| 0 |

1 |

1 |

1 |

0 |

1 |

| 1 |

0 |

1 |

0 |

1 |

1 |

| 1 |

1 |

0 |

1 |

1 |

1 |

|

|

| Входы |

Выходы |

|

|

|

|

|

|

| 0 |

0 |

1 |

0 |

0 |

0 |

| 0 |

1 |

0 |

1 |

0 |

0 |

| 1 |

0 |

0 |

0 |

1 |

0 |

| 1 |

1 |

0 |

0 |

0 |

1 |

|

|

| Входы |

Выходы |

|

|

|

|

|

|

| 0 |

0 |

1 |

1 |

0 |

0 |

| 0 |

1 |

0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

0 |

1 |

|

Выберите УГО для функциональной схемы дешифратора:

Какова разрядность базового дешифратора, если каскад на 6 входных линий состоит из трёх очередей?

|

три входа |

|

два входа |

|

восемь выходов |

|

четыре выхода |

Какова разрядность базового дешифратора, если каскад на 64 выхода состоит из трёх очередей?

|

два входа |

|

три входа |

|

восемь выходов |

|

четыре выхода |

Сколько выходных линий будет у каскада дешифраторов, содержащего 3 очереди, если на дешифраторы каждой очереди подключаются по 3 входных сигнала?

|

восемь |

|

тридцать две |

|

пятьсот двенадцать |

|

сто двадцать восемь |

Сколько очередей будет содержать каскад на 64 выхода, если в нашем распоряжении только 2-входовые дешифраторы?

|

две |

|

три |

|

восемь |

|

тридцать две |

Сколько очередей будет содержать каскад на 4 входа, если в нашем распоряжении только дешифраторы на 4 выхода?

|

одну |

|

две |

|

три |

|

четыре |

Сколько нужно мультиплексоров на 2 адресных входа для построения схемы «1 из 32″:

|

8 |

|

16 |

|

32 |

|

64 |

Выберите таблицу истинности для УГО мультиплексора :

|

| Е |

А2 |

А1 |

А0 |

Y |

| 1 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

1 |

0 |

| 1 |

0 |

1 |

0 |

0 |

| 1 |

0 |

1 |

1 |

0 |

| 1 |

1 |

0 |

0 |

0 |

| 1 |

1 |

0 |

1 |

0 |

| 1 |

1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

0 |

| 0 |

0 |

0 |

0 |

D0 |

| 0 |

0 |

0 |

1 |

D1 |

| 0 |

0 |

1 |

0 |

D2 |

| 0 |

0 |

1 |

1 |

D3 |

| 0 |

1 |

0 |

0 |

D4 |

| 0 |

1 |

0 |

1 |

D5 |

| 0 |

1 |

1 |

0 |

D6 |

| 0 |

1 |

1 |

1 |

D7 |

|

|

| Е |

А2 |

А1 |

А0 |

Y |

| 0 |

0 |

0 |

0 |

0 |

| 1 |

0 |

0 |

1 |

0 |

| 0 |

0 |

1 |

0 |

0 |

| 1 |

0 |

1 |

1 |

0 |

| 0 |

1 |

0 |

0 |

0 |

| 1 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

0 |

| 0 |

0 |

0 |

0 |

D0 |

| 1 |

0 |

0 |

1 |

D1 |

| 0 |

0 |

1 |

0 |

D2 |

| 1 |

0 |

1 |

1 |

D3 |

| 0 |

1 |

0 |

0 |

D4 |

| 1 |

1 |

0 |

1 |

D5 |

| 0 |

1 |

1 |

0 |

D6 |

| 1 |

1 |

1 |

1 |

D7 |

|

|

| Е |

А2 |

А1 |

А0 |

Y |

| 0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

0 |

1 |

0 |

| 0 |

0 |

1 |

0 |

0 |

| 0 |

0 |

1 |

1 |

0 |

| 1 |

1 |

0 |

0 |

0 |

| 1 |

1 |

0 |

1 |

0 |

| 1 |

1 |

1 |

0 |

0 |

| 1 |

1 |

1 |

1 |

0 |

| 0 |

0 |

0 |

0 |

D0 |

| 0 |

0 |

0 |

1 |

D1 |

| 0 |

0 |

1 |

0 |

D2 |

| 0 |

0 |

1 |

1 |

D3 |

| 1 |

1 |

0 |

0 |

D4 |

| 1 |

1 |

0 |

1 |

D5 |

| 1 |

1 |

1 |

0 |

D6 |

| 1 |

1 |

1 |

1 |

D7 |

|

|

| Е |

А2 |

А1 |

А0 |

Y |

| 0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

0 |

1 |

0 |

| 0 |

0 |

1 |

0 |

0 |

| 0 |

0 |

1 |

1 |

0 |

| 0 |

1 |

0 |

0 |

0 |

| 0 |

1 |

0 |

1 |

0 |

| 0 |

1 |

1 |

0 |

0 |

| 0 |

1 |

1 |

1 |

0 |

| 1 |

0 |

0 |

0 |

D0 |

| 1 |

0 |

0 |

1 |

D1 |

| 1 |

0 |

1 |

0 |

D2 |

| 1 |

0 |

1 |

1 |

D3 |

| 1 |

1 |

0 |

0 |

D4 |

| 1 |

1 |

0 |

1 |

D5 |

| 1 |

1 |

1 |

0 |

D6 |

| 1 |

1 |

1 |

1 |

D7 |

|

Сколько информационных линий будет у каскада мультиплексоров, состоящего в первой очереди из четырёх мультиплексоров «1 из 16″?

|

128 |

|

64 |

|

16 |

|

256 |

Выберите УГО мультиплексора на 4 адресных входа с прямым разрешающим сигналом:

Выберите таблицу истинности, соответствующую синхронному RS-триггеру:

|

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

|

| 0 |

0 |

0 |

|

|

Хранение ранее записанной информации |

| 0 |

0 |

1 |

| 0 |

1 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

0 |

|

|

Хранение ранее записанной информации |

| 1 |

0 |

1 |

0 |

1 |

Сброс триггера |

| 1 |

1 |

0 |

1 |

0 |

Установка триггера |

| 1 |

1 |

1 |

0 |

0 |

Неустойчивое состояние |

|

|

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

| 0 |

0 |

0 |

0 |

Неустойчивое состояние |

| 0 |

1 |

1 |

0 |

Установка триггера |

| 1 |

0 |

0 |

1 |

Сброс триггера |

| 1 |

1 |

|

|

Хранение ранее записанной информации |

|

|

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

| 0 |

0 |

Q_{i-1} |

|

Хранение ранее записанной информации |

| 0 |

1 |

|

|

Хранение ранее записанной информации |

| 1 |

0 |

0 |

1 |

Сброс триггера |

| 1 |

1 |

1 |

0 |

Установка триггера |

|

|

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

| 0 |

0 |

|

|

Хранение ранее записанной информации |

| 0 |

1 |

0 |

1 |

Сброс триггера |

| 1 |

0 |

1 |

0 |

Установка триггера |

| 1 |

1 |

0 |

0 |

Неустойчивое состояние |

|

Выберите тип триггера по УГО:

|

RS-триггер в базисе И-НЕ |

|

синхронный RS-триггер |

|

RS-триггер в базисе ИЛИ-НЕ |

|

D-триггер |

Выберите УГО RS-триггера в базисе ИЛИ-НЕ:

Выберите тип триггера по его таблице истинности

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

| 0 |

0 |

|

|

Хранение ранее записанной информации |

| 0 |

1 |

0 |

1 |

Сброс триггера |

| 1 |

0 |

1 |

0 |

Установка триггера |

| 1 |

1 |

0 |

0 |

Неустойчивое состояние |

|

D-триггер |

|

RS-триггер в базисе ИЛИ-НЕ |

|

синхронный RS-триггер |

|

RS-триггер в базисе И-НЕ |

Выберите тип триггера по его таблице истинности

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

| 0 |

0 |

0 |

0 |

Неустойчивое состояние |

| 0 |

1 |

1 |

0 |

Установка триггера |

| 1 |

0 |

0 |

1 |

Сброс триггера |

| 1 |

1 |

|

|

Хранение ранее записанной информации |

|

RS-триггер в базисе ИЛИ-НЕ |

|

RS-триггер в базисе И-НЕ |

|

D-триггер |

|

синхронный RS-триггер |

Выберите таблицу истинности, соответствующую УГО триггера

|

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

| 0 |

0 |

|

|

Хранение ранее записанной информации |

| 0 |

1 |

0 |

1 |

Сброс триггера |

| 1 |

0 |

1 |

0 |

Установка триггера |

| 1 |

1 |

0 |

0 |

Неустойчивое состояние |

|

|

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

| 0 |

0 |

0 |

0 |

Неустойчивое состояние |

| 0 |

1 |

1 |

0 |

Установка триггера |

| 1 |

0 |

0 |

1 |

Сброс триггера |

| 1 |

1 |

|

|

Хранение ранее записанной информации |

|

|

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

| 0 |

0 |

|

|

Хранение ранее записанной информации |

| 0 |

1 |

|

|

Хранение ранее записанной информации |

| 1 |

0 |

0 |

1 |

Сброс триггера |

| 1 |

1 |

1 |

0 |

Установка триггера |

|

|

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

|

| 0 |

0 |

0 |

|

|

Хранение ранее записанной информации |

| 0 |

0 |

1 |

| 0 |

1 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

0 |

|

|

Хранение ранее записанной информации |

| 1 |

0 |

1 |

0 |

1 |

Сброс триггера |

| 1 |

1 |

0 |

1 |

0 |

Установка триггера |

| 1 |

1 |

1 |

0 |

0 |

Неустойчивое состояние |

|

Выбрать УГО регистра по таблице истинности

|

|

Режим работы |

| 1 |

|

Передача инверсной информации |

| 0 |

|

Хранение ранее записанной инверсной информации |

Выберите дешифратор, необходимый для адресации шестнадцати 8-разрядных регистров:

Сколько 16-разрядных регистров будет в схеме СОЗУ на восемь 16-разрядных чисел?

|

64 |

|

16 |

|

8 |

|

32 |

Найдите соответствие таблиц истинности регистров и их УГО:

-

|

|

Режим работы |

| 0 |

|

Передача информации |

| 1 |

|

Хранение ранее записанной информации |

-

|

|

Режим работы |

| 1 |

|

Передача информации |

| 0 |

|

Хранение ранее записанной информации |

-

|

|

Режим работы |

| 1 |

|

Передача инверсной информации |

| 0 |

|

Хранение ранее записанной инверсной информации |

-

|

|

Режим работы |

| 1 |

|

Хранение ранее записанной инверсной информации |

| 0 |

|

Передача инверсной информации |

Какому десятичному коду соответствует код  , вызывающий в приведенной схеме выдачу сигнала переноса

, вызывающий в приведенной схеме выдачу сигнала переноса  ?

?

|

3 |

|

7 |

|

5 |

|

4 |

Какая функция ИМС соответствует схеме

|

RG |

|

SM |

|

CT |

|

Т |

Укажите код минимальной суммы на выходе сумматора

Какое словесное описание соответствует условному графическому обозначению (функция ИМС не показана)

|

регистр для выбора одного из двух 4-разрядных чисел |

|

мультиплексор, выбирающий одно из двух 4-разрядных чисел |

|

сумматор для 4-разрядных чисел |

|

регистр для хранения двух 4-разрядных чисел |

Укажите код минимальной суммы на выходе сумматора

Какова сумма на выходе сумматора?

|

5 |

|

6 |

|

4 |

|

3 |

Укажите код максимальной суммы на выходе сумматора

Какая функция ИМС соответствует схеме

|

RG |

|

CT |

|

SM |

|

Т |

Укажите правильные коды на выходе сумматора

Укажите правильные коды на выходе сумматора

Найдите соответствие между названием ИМС и обозначением функции, которую она выполняет?

- Триггер.

- Сумматор.

- Счетчик.

- Дешифратор.

Какой максимальный код адреса можно подать на адресные входы ИМС памяти

|

111111111102 |

|

1111111111102 |

|

111111111112 |

|

1111111111112 |

Запоминающий элемент статического ОЗУ — это

|

схема из двух биполярных транзисторов, охваченных положительной обратной связью |

|

биполярный транзистор и плавкая вставка |

|

один полевой транзистор |

|

три полевых транзистора |

Какое словесное описание соответствует условному графическому обозначению

|

ПЗУ для хранения 4096 бит информации |

|

статическое ОЗУ на 4К бит информации |

|

статическое ОЗУ на 4К байт информации |

|

динамическое ОЗУ на 4К бит информации |

Какое словесное описание соответствует условному графическому обозначению

|

динамическое ОЗУ на 1М бит информации |

|

динамическое ОЗУ на 16К бит информации |

|

динамическое ОЗУ на 1К бит информации |

|

ПЗУ для хранения 1024 бит информации |

Какой максимальный код адреса можно подать на адресные входы ИМС памяти

|

1111111102 |

|

11111112 |

|

111111102 |

|

111111112 |

Найдите соответствие между УГО (функция ИМС не показана) и обозначением функции, которую она выполняет

Выделите названия типов ЗУ, которые могут быть только полупроводниковыми:

|

ПЗУ |

|

ОЗУ |

|

СОЗУ |

|

БЗУ |

Какая из записей числа может быть воспринята как двоичный код?

|

10110011 |

|

101010201 |

|

2010101 |

|

1012101 |

Выберите десятичный код, соответствующий восьмеричному коду 05.

|

13 |

|

85 |

|

15 |

|

5 |

Выберите правильный результат двоичного сложения

| + |

1 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

| ? |

? |

? |

? |

? |

? |

? |

|

1101100 |

|

1010010 |

|

1011010 |

|

1011101 |

Выберите двоичный код, соответствующий десятичному числу 49.

|

110001 |

|

11001 |

|

1101 |

|

1100001 |

Выберите правильный результат двоичного вычитания

| - |

1 |

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

|

? |

? |

? |

? |

? |

? |

|

101101 |

|

010001 |

|

110001 |

|

101100 |

Выберите правильный результат двоичного сложения

| + |

1 |

0 |

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

| ? |

? |

? |

? |

? |

? |

? |

|

1000011 |

|

1100011 |

|

1100111 |

|

100011 |

Выделите таблицу истинности, соответствующую схеме ПЗУ

|

| Адрес |

Данные |

| 00 |

1100 |

| 01 |

1011 |

| 10 |

1000 |

| 11 |

1101 |

|

|

| Адрес |

Данные |

| 00 |

0010 |

| 01 |

0111 |

| 10 |

0100 |

| 11 |

0011 |

|

|

| Адрес |

Данные |

| 00 |

0011 |

| 01 |

0100 |

| 10 |

0111 |

| 11 |

0010 |

|

|

| Адрес |

Данные |

| 00 |

1101 |

| 01 |

1000 |

| 10 |

1011 |

| 11 |

1100 |

|

Выделите таблицу истинности, соответствующую схеме ПЗУ

|

| Адрес |

Данные |

| 00 |

1000 |

| 01 |

1000 |

| 10 |

1011 |

| 11 |

1111 |

|

|

| Адрес |

Данные |

| 00 |

0000 |

| 01 |

0100 |

| 10 |

0111 |

| 11 |

0111 |

|

|

| Адрес |

Данные |

| 00 |

1011 |

| 01 |

1101 |

| 10 |

0010 |

| 11 |

0100 |

|

|

| Адрес |

Данные |

| 00 |

0100 |

| 01 |

0010 |

| 10 |

1101 |

| 11 |

1011 |

|

Сколько информации можно зхранить в ИМС памяти

|

1К бит |

|

1К байт |

|

512 байт |

|

1024 байта |

Каков информационный объём ИМС памяти

|

1К х 8 |

|

10К х 8 |

|

1024 х 8 |

|

512 х 8 |

Выделите таблицу истинности, соответствующую схеме ПЗУ

|

| Адрес |

Данные |

| 00 |

11 |

| 01 |

11 |

| 10 |

11 |

| 11 |

00 |

|

|

| Адрес |

Данные |

| 00 |

11 |

| 01 |

00 |

| 10 |

00 |

| 11 |

00 |

|

|

| Адрес |

Данные |

| 00 |

00 |

| 01 |

00 |

| 10 |

00 |

| 11 |

11 |

|

|

| Адрес |

Данные |

| 00 |

00 |

| 01 |

11 |

| 10 |

11 |

| 11 |

11 |

|

Сколько информации можно хранить в ИМС памяти

|

8К бит |

|

4К байт |

|

4К бит |

|

8К байт |

Выделите ИМС информационного объёма 512 байт

Сколько ИМС указанного вида нужно соединить для обеспечения адресации к 2К одноразрядным числам?

|

4 |

|

8 |

|

2 |

|

16 |

Выберите дешифратор, необходимый для выбора ИМС указанного типа памяти в схеме информационного объёма 16К байт.

Сколько ИМС указанного вида нужно соединить для обеспечения возможности работы с 8-разрядными числами?

|

1 |

|

2 |

|

8 |

|

4 |

Выберите дешифратор, необходимый для выбора ИМС указанного типа памяти в схеме информационного объёма 16К байт.

Выберите дешифратор для адресации к восьми ИМС памяти.

Найдите соответствие ИМС дешифратора и УГО ПЗУ, которые необходимы для синтеза схемы памяти объёмом 16К байт:

Выберите тип буферной части логического элемента для заданной схемы

|

буфер с активной нагрузкой |

|

буфер с разрешающим сигналом |

|

буфер на три состояния |

|

буфер с открытым коллектором |

Сколько транзисторов содержит 3-входовая схема И-НЕ технологии КМОП?

|

12 |

|

3 |

|

6 |

|

9 |

Выберите схему инвертора nМОП

Выберите правильное логического элемента для заданной схемы

|

НЕ технологии КМОП |

|

ИЛИ технологии КМОП |

|

И-НЕ технологии pМОП |

|

ИЛИ-НЕ технологии nМОП |

Сколько много-эмиттерных транзисторов содержит схема инвертора ТТЛ?

|

3 |

|

1 |

|

2 |

|

0 |

Выберите УГО триггера по его таблице истинности

| Управляющие сигналы |

Состояние выходов |

Режим работы |

|

|

|

|

| 0 |

0 |

|

|

Хранение ранее записанной информации |

| 0 |

1 |

|

|

Хранение ранее записанной информации |

| 1 |

0 |

0 |

1 |

Сброс триггера |

| 1 |

1 |

1 |

0 |

Установка триггера |

Выберите запись прямого кода, соответствующую десятичному числу (-33).

|

0.100001 |

|

1.100001 |

|

0.1000001 |

|

1.10001 |

Сколько транзисторов содержит инвертор технологии nМОП?

|

2 |

|

3 |

|

1 |

|

4 |

, вызывающий в приведенной схеме выдачу сигнала переноса

, вызывающий в приведенной схеме выдачу сигнала переноса  ?

?

Добавить комментарий

Для отправки комментария вы должны авторизоваться.